16年初入某公司,像一个好奇的猫,在闲来无事翻看早期案例时,看到过某部门为某老款产品的LDO电容更换为MLCC电容后,产品故障率超标的事件。

现在试着回忆一下,并把机理讲述清楚。

背景

LDO电路设计表面上看起来很简单,输入和输出各接一个电容就行了。没有开关电源那样的开关噪声,纹波抑制特性又好,自身噪声又小,故在小信号场景上比较受欢迎。

该项目使用了一款老型号LDO,早期产品出货很多,故障率中规中矩。到了产品更新换代的时候,为了节省成本与布局面积,将电容更改为MLCC,彼时并没有投入过多关注,换个电容而已,能有什么幺蛾子?

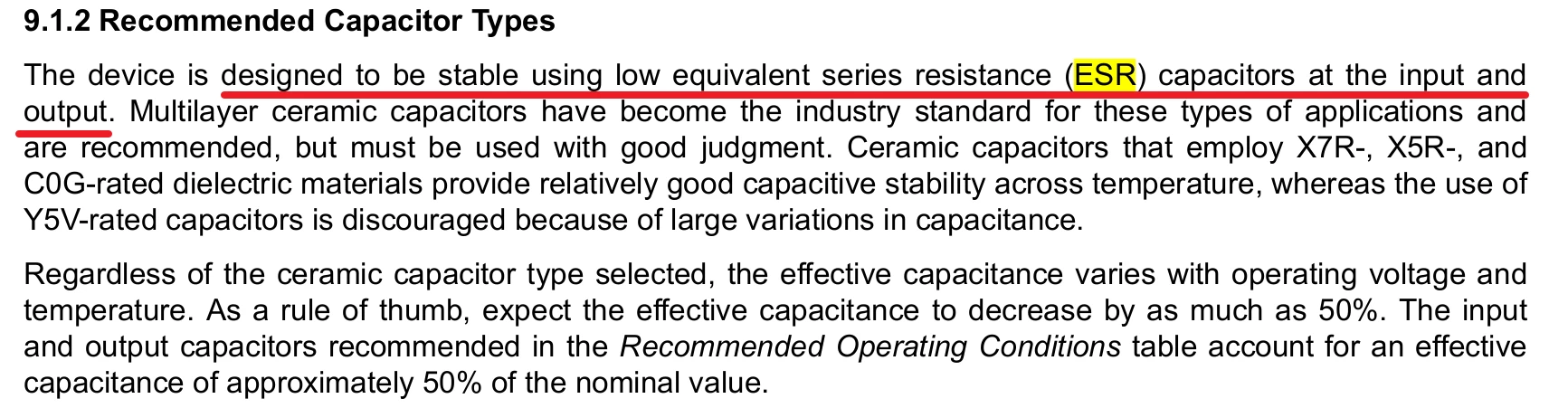

但市场的故障率飙升反馈着实让人大吃一惊,遂要查找根因。在debug时,部分机器能测到LDO纹波异常偏高,甚至有上百mV之多,可谓是波涛汹涌,大致如下图所示。

查来查去才发现,是因为更换后的MLCC电容ESR偏低较多,破坏了原有的零点补偿,导致相位裕度不足、振荡发生的概率增加,影响负载模块,故FFR飙升。

原理

LDO业已问世很长时间,早期的LDO在开发时,世界上还没有大规模流行低ESR电容(典型器件MLCC),所以是按照以高ESR Cout电容而设计的误差放大器的相位补偿。

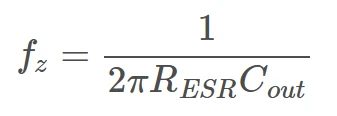

如下图,早期的LDO中通常有三个极点(Pole):

- 主极点,Dominant Pole,简称P(DOM),由误差放大器内部补偿电容形成,几百Hz附近,控制低频增益,重要性较强。

- 负载极点,简称P(load),由Cout与负载共同形成。

- 功率管栅极极点,简称P(PASS),由功率管栅极寄生电容+驱动电阻所致,引入第三个滞后。

我们都知道LDO是一个负反馈系统,为了在任何负载条件下都能稳定工作(不振荡),其环路的相位裕度必须足够才好,最好在60°以上。有点像你在社会上混,钱包越鼓越安心,越少则越容易焦虑、炸毛。

而现在,极点起到的是滞后作用,每个极点最大能贡献90°的滞后,而三个极点叠加,最大能引入270°的相移。

别说余量了,几个极点的叠加,极有可能直接形成360°的正反馈(极点形成180°滞后 + 误差放大器180°反相),如果此时系统增益不低于0dB,则势必会振荡。

相比于极点的滞后,零点(Zero)有超前的作用,所以这种老式LDO最常见的补偿方法是在系统中插入一个零点,以补偿相移和滚降速度,起到救火的作用。

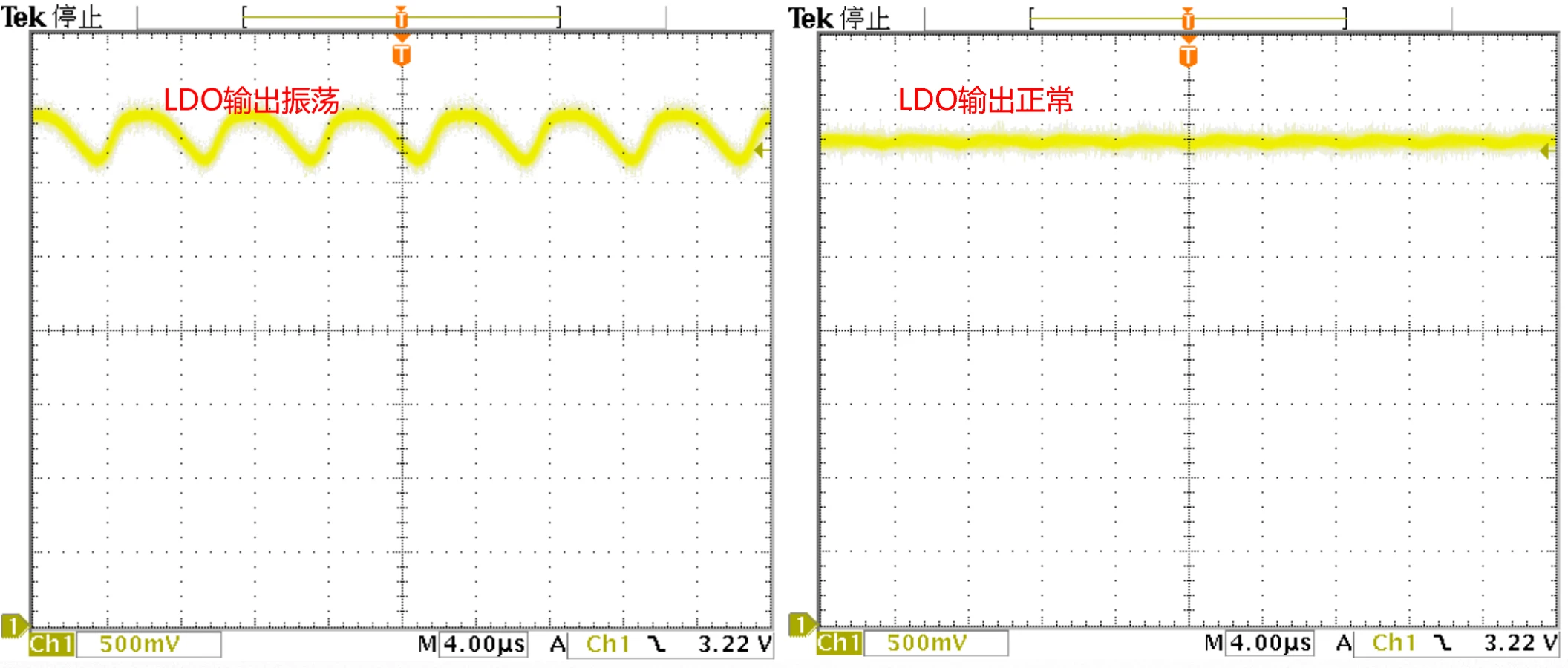

通常最简单、最低成本的方案是巧妙利用Cout的ESR和Cout的容值产生一个零点,该零点的表达式如下:

如下图,通过对比可以看出,这个零点确实能拉回一部分被极点拖下去的相位,老式LDO非常依赖这个零点来提升相位裕度。

钽电容ESR通常在0.5Ω - 3Ω,铝电解电容的ESR更大一些,零点频率尚在预期的频率范围内,可抵消其他极点造成的相位滞后。

而MLCC则有显著不同,其ESR通常为几毫欧到几十毫欧,这就导致了零点频率偏高,覆盖不上中频段的相位滑坡,起不到预期的补偿作用,于是原本稳定的系统就崩了。

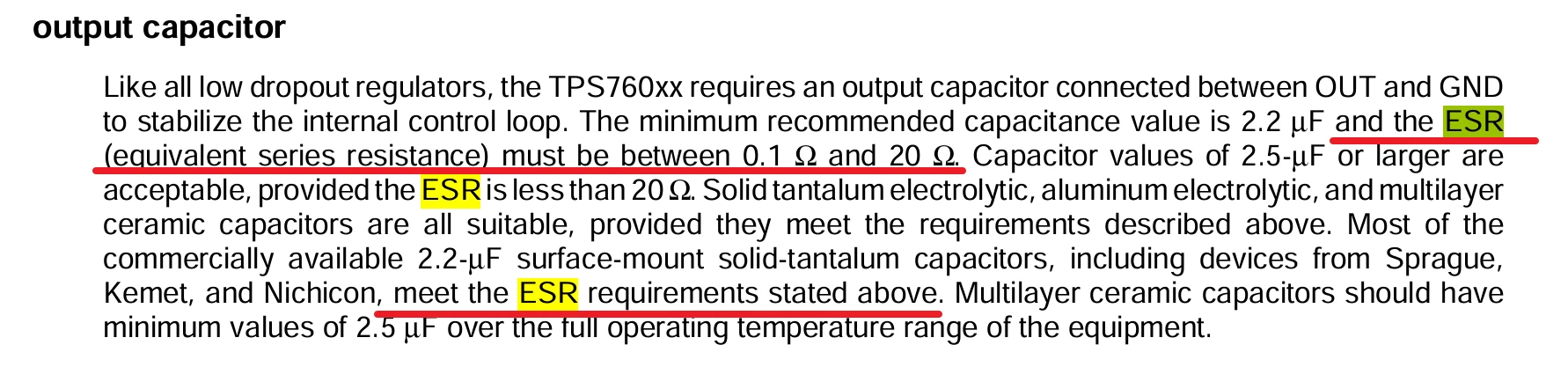

老式的LDO在规格书中也有写清楚ESR的范围,以TI的TPS76030 LDO为例,有规定最小值,让工程师不要乱搞,如下图所示。

现代LDO

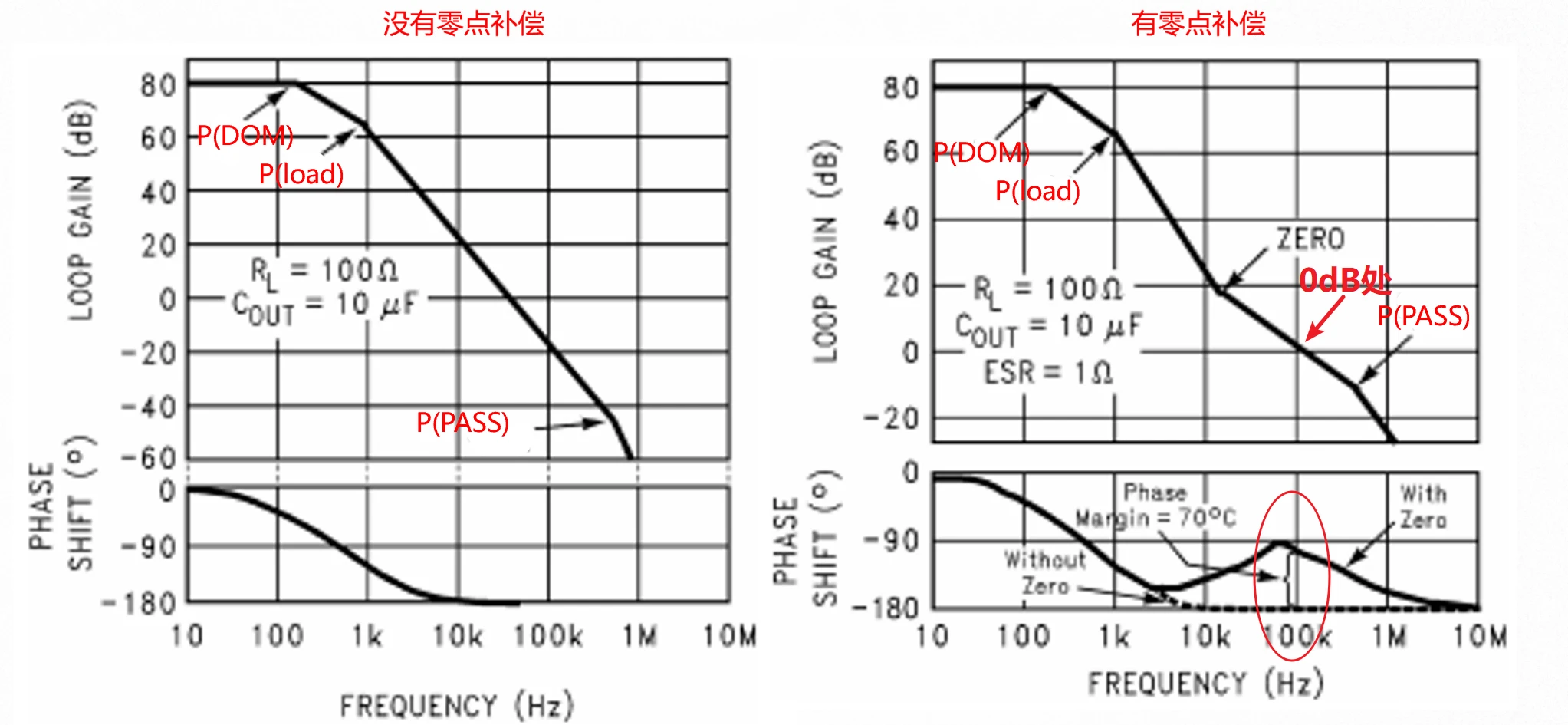

早期的LDO搭配低ESR电容,零点频率过高,起不到补偿的作用,容易振荡。现在MLCC电容广泛铺开,因此现在的LDO在设计上对此有改进,通过在内部进行零点补偿,降低了外部电容的影响。

以TI的TPS7A25 LDO为例,其在datasheet中明确表述了,低ESR对电路来说是稳定的,无需过分关心输出电容的ESR。